# International Journal of Engineering Technologies and Management Research

ISSN: 2454-1907

A Knowledge Repository

# A SPURIOUS-POWER SUPPRESSION TECHNIQUE FOR DSP APPLICATIONS

Dr. M.S. Gaikwad <sup>1</sup>, Vishal Shivaji Bari <sup>2</sup>

<sup>1, 2</sup> Electronics and telecommunication, Sinhgad Institute of Technology, India

#### **Abstract:**

To assist a solution to the problem of the test environment spanning multiple platforms, this This report presents the arrangement examination and employments of a Spurious-Power Suppression Technique (SPST) which can essentially decrease the power dissipating of combinational VLSI diagrams for intuitive media/DSP purposes. The proposed SPST disengages the target diagrams into two segments, i.e., Most Significant Part (MSP) and the Least Significant Part (LSP), and turns off the MSP when it doesn't impact the estimation results to save control. Also, this paper proposes a one of a kind glitch-decreasing strategy to filter through inconsequential trading power by announcing the data movements after the data transient period. This paper gets adaptable versatile multimedia functional unit (VMFU), to evaluate the proposed SPST. These two arrangement cases have exceptionally phenomenal hardware setups, thusly, the affirmation issues of the SPST on each blueprint in like manner incredibly shift from each other. The VMFU has six routinely used media/DSP limits, specifically, extension, subtraction, increment, MAC, presentation, and aggregate of-add up to qualification.

Keywords: MAC; VMFU; SPST; DSP.

**Cite This Article:** Dr. M.S. Gaikwad, and Vishal Shivaji Bari. (2018). "A SPURIOUS-POWER SUPPRESSION TECHNIQUE FOR DSP APPLICATIONS." *International Journal of Engineering Technologies and Management Research*, 5(6), 80-86. DOI: https://doi.org/10.29121/ijetmr.v5.i6.2018.247.

#### 1. Introduction

One of the going with challenges in outlining ICs for compact electrical gadgets is dropping down the power utilization to drag out the working time based on given constrained vitality supply from batteries. Attributable to the lively improvement of the remote framework and the individual electronic gadgets like video cell phones, versatile TV sets, PDAs, and so forth., sight and sound and DSP applications have been received in remote conditions. Be that as it may, propelled mixed media/DSP applications.

Different systems have been produced for lessening the power utilization of VLSI outlines, including voltage scaling, exchanged capacitance decrease, clock gating, shut down procedures, edge voltage controlling, various supply voltages, and dynamic voltage recurrence scaling. These low-control systems have been turned out to be proficient to certain detriment and are material to media/DSP plans. Among these low-control methods, a promising heading for fundamentally

lessening power utilization is diminishing the dynamic power which rules add up to control scattering. Thus, this paper builds up an extraordinary failure control strategy which can lessen dynamic power. The proposed low-control procedure can be utilized with a portion of the previously mentioned strategies without clashes to additionally diminish the power utilization of the sight and sound/DSP outlines. The current works that decrease the dynamic power utilization by limiting the exchanged capacitance incorporate the plans in. The plan proposes an idea called in partially guarded computation (PGC), which isolates the math units, e.g., adders and multipliers, into two sections and turns off the unused part to limit the power utilization.

In this investigates the hardware of actualizing the alleged Spurious-Power Suppression Technique (SPST), and in addition two plan cases for the sight and sound/DSP applications. The SPST can significantly decrease the power dissemination of combinational VLSI outlines for media/DSP applications. This situation makes a decent chance to limit the additional power scattering by extravagantly streamlining the hardware. From the perspective of rationale outline, the adders/subtractors in the change coding configuration are isolated into two sections, i.e., the Most Significant Part (MSP) and the Least Significant Part (LSP), and the info information of the MSP circuits are hooked at whatever point they don't impact the calculation comes about. In addition, recognition rationale and SE units are acquainted in the proposed SPST with decide the powerful scopes of the operands and make up for the sign signs of the MSP, individually. In spite of the fact that this idea is like the PGC, productively actualizing the idea and showing its impacts on control sparing in genuine circuits stays testing. To overcome this plan challenge, this paper investigates the fundamental reasons of the event of spurious power and shows an intensive examination for effectively actualizing SPST adders/subtractors. From those investigations and the actualizing background, we find the harm of the glitches to the combinational circuits and further propose.

### 2. Proposed Work

Besides the explanations presented in our former studies, this report provides further illustrations of the proposed SPST as described in the following sections.

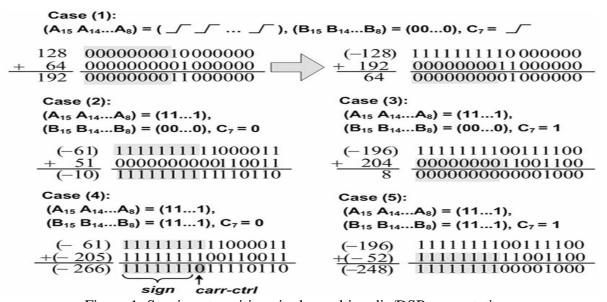

Figure 1: Spurious transitions in the multimedia/DSP computations

ISSN: 2454-1907 DOI: 10.5281/zenodo.1313090

## 2.1. Theoretical Analysis and Logic Derivation

To delineate the reason of those spurious flag changes we investigate five instances of 16-bit augmentations as appeared in Fig. 1. The instances of trading the operands An and B in increments prompt the same spurious changes with those appeared in Fig. 1. Thus, there is most likely no other case past these five in view of this plan. The principal case delineates a transient state in which spurious changes of convey signals happen in the MSP, in spite of the fact that the last aftereffect of the MSP is unaltered. Then, the second and third cases depict circumstances including one negative operand including another positive operand without and with convey in from the LSP, individually. In addition, the fourth and fifth cases exhibit the expansion of two negative operands without and with convey in from the LSP, separately. In those cases, the consequences of MSP are unsurprising; thusly, the calculations in MSP are pointless and can be disregarded. Killing those spurious calculations not exclusively can spare the power utilization inside the adder/subtractor in the present stage yet in addition can diminish the glitchingclamors which cause control wastage inside the number juggling circuits in the following stage. From the examination of Fig. 1, we are roused to propose the SPST that isolates the adder/subtractor into two sections and after that locks the information of the MSP at whatever point they don't influence the calculation comes about. The SPST can be extended to be a fine-grain plot in which the snake/subtractor is partitioned into more than two sections. In any case, the equipment intricacy of the enlarged circuits, for example, the discovery rationale unit, the information locks, and the SE unit increments drastically. In view of a snake/subtractor case, we really find that the power cost caused by the expanded circuits is bigger than the power lessening in a tripartitioned conspire. This is the reason we propose a bipartitioned SPST conspire in this To know whether the MSP influences the calculation brings about the bipartitioned SPST plot, a discovery rationale unit must be utilized to distinguish the compelling info ranges. The Boolean consistent conditions appeared as takes after express the behavioral standards of the identification rationale unit.

| carr-ctrl          |    | $C_{LSP}, A_{and}, A_{nor}$ |     |     |     |     |     |     |     |  |

|--------------------|----|-----------------------------|-----|-----|-----|-----|-----|-----|-----|--|

|                    |    | 000                         | 001 | 011 | 010 | 100 | 101 | 111 | 110 |  |

| $B_{and}, B_{nor}$ | 00 | 0                           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

|                    | 01 | 0                           | 0   | 0   | 1   | 0   | 1   | 0   | 0   |  |

|                    | 11 | 0                           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

|                    | 10 | 0                           | 1   | 0   | 0   | 0   | 0   | 0   | 1   |  |

(a)

| sign               |    | $C_{LSP}, A_{and}, A_{nor}$ |     |     |     |     |     |     |     |  |

|--------------------|----|-----------------------------|-----|-----|-----|-----|-----|-----|-----|--|

|                    |    | 000                         | 001 | 011 | 010 | 100 | 101 | 111 | 110 |  |

| $B_{and}, B_{nor}$ | 00 | 0                           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

|                    | 01 | 0                           | 0   | 0   | 1   | 0   | 0   | 0   | 0   |  |

|                    | 11 | 0                           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

|                    | 10 | 0                           | 1   | 0   | 1   | 0   | 0   | 0   | 1   |  |

(b) Figure 2: K-map of carry-ctrl & Sign

$$carr - ctrl = \overline{C_{\text{LSP}}} \times \overline{A_{\text{and}}} \times A_{\text{nor}} \times B_{\text{and}} \times \overline{B_{\text{nor}}} + \overline{C_{\text{LSP}}} \times A_{\text{and}} \times \overline{A_{\text{nor}}} \times \overline{B_{\text{and}}} \times B_{\text{nor}} + C_{\text{LSP}} \times \overline{A_{\text{and}}} \times A_{\text{nor}} \times \overline{B_{\text{and}}} \times B_{\text{nor}} + C_{\text{LSP}} \times A_{\text{and}} \times \overline{A_{\text{nor}}} \times B_{\text{and}} \times \overline{B_{\text{nor}}} = \overline{C_{\text{LSP}}} \times (\overline{A_{\text{and}}} \times B_{\text{and}} + A_{\text{and}} \times \overline{B_{\text{and}}}) \times (A_{\text{and}} \times B_{\text{and}} + A_{\text{and}} \times B_{\text{nor}} + A_{\text{nor}} \times B_{\text{and}} + A_{\text{nor}} \times B_{\text{nor}}) + C_{\text{LSP}} \times (A_{\text{and}} \times B_{\text{and}} + \overline{A_{\text{and}}} \times \overline{B_{\text{and}}}) \times (A_{\text{and}} \times B_{\text{and}} + A_{\text{and}} \times B_{\text{nor}} + A_{\text{nor}} \times B_{\text{and}} + A_{\text{nor}} \times B_{\text{and}}) \times (A_{\text{and}} \times B_{\text{nor}}) (C_{\text{LSP}} \oplus A_{\text{and}} \oplus B_{\text{and}}) \times (A_{\text{and}} + A_{\text{nor}}) \times (B_{\text{and}} + B_{\text{nor}})$$

$$(7)$$

Figure 3: Equation of Carry-ctrl

$$sign = \overline{C_{\text{LSP}}} \times (\overline{A_{\text{and}}} \times A_{\text{nor}} \times B_{\text{and}} \times \overline{B_{\text{nor}}} + A_{\text{and}} \times \overline{A_{\text{nor}}} \times \overline{B_{\text{and}}} \times B_{\text{nor}} + A_{\text{and}} \times \overline{A_{\text{nor}}} \times B_{\text{and}} \times \overline{B_{\text{nor}}})$$

$$+ C_{\text{LSP}} \times A_{\text{and}} \times \overline{A_{\text{nor}}} \times B_{\text{and}} \times \overline{B_{\text{nor}}}$$

$$= \overline{C_{\text{LSP}}} \times (\overline{A_{\text{and}}} \times B_{\text{and}} + A_{\text{and}})$$

$$+ C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

$$= \overline{C_{\text{LSP}}} \times (A_{\text{and}} + B_{\text{and}}) + C_{\text{LSP}} \times A_{\text{and}} \times B_{\text{and}}$$

Figure 4: Equation of Sign

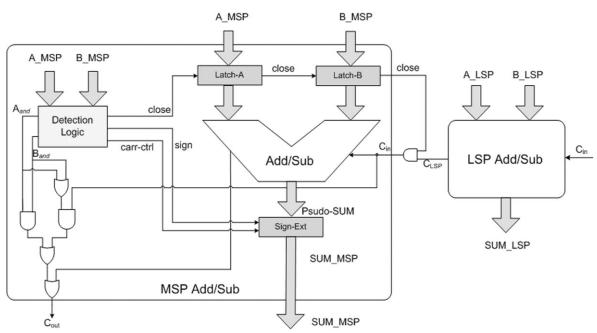

Figure 5: Low power adder/subtractor design adopting proposed SPST

Where A[m]and B[n], individually, signify the m th bit of the operand An and the n th bit of the operand B, and, separately, indicate the MSP parts, i.e., the ninth piece to the sixteenth piece, of the operands An and B in the cases appeared in Fig. 3. At the point when the bits in Amsp and additionally Bmsp in are each of the ones, the estimation of An and as well as that of B and, individually, wind up plainly one, while when the bits in Amsp or potentially Bmsp in are every one of the zeros, the estimation of Anor and additionally that of B nor, separately, transform into one. Being one of the three yields of the location rationale unit, close means whether the MSP circuits can be dismissed or not. Contrasted and the utilization of transmission doors to hook the data sources, this plan can keep the voltage-drop issues caused by the gliding associated focuses after the MSP circuits are shut for a generally long traverse of time. The approaches to make up for the sign bits of the figuring comes about are likewise appeared in the event. In like manner, we determine the KARNAUGH maps which prompt the Boolean consistent conditions.

# 3. Design Methodology

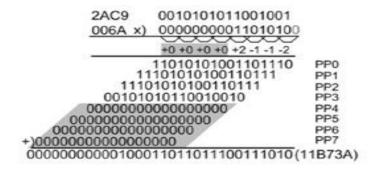

Figure 6: Illustration of multiplication using modified Booth encoding

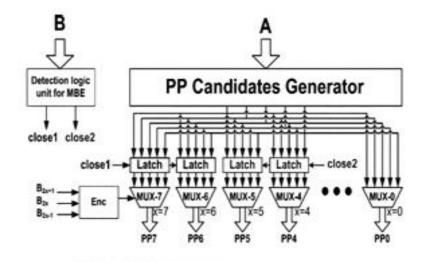

Figure 7: SPST modified Booth encoder

The plan case utilizing the proposed SPST is the VMFU, which is developed based on a changed Booth encoding multiplier. The proposed VMFU can process six sorts of number-crunching operations, i.e., expansion, subtraction, augmentation, MAC, interjection, and SAD, which are

every now and again utilized as a part of sight and sound/DSP calculations. There are three recognizing plan contemplations in outlining the VMFU, as recorded as takes after.

# 3.1. Applying the SPST to the Modified Booth Encoder

Fig.6 demonstrates a calculation case of Booth duplicating two numbers "2AC9hex" and "006Ahex," where the shadow indicates that the numbers in this piece of Booth increase are every one of the zeros with the goal that this piece of the calculations can be ignored. Sparing those calculations can fundamentally lessen the power utilization caused by the transient signs. As indicated by the examination of the duplication appeared in Fig.6, we propose the SPST altered Booth encoder which incorporates a location unit, as appeared in Fig.7.From one of the two operands, e.g., the operand A, the fractional item (PP) competitor generator creates five hopefuls of the incomplete items, i.e., {-2A, - A,0,A,2A}, which are then chosen by the Booth encoding aftereffects of the other operand, i.e., the operand B. Then, the discovery unit has the second one of the two operands, i.e., the operand B for this situation, as its contribution to choose whether the Booth encoder incorporates repetitive calculations. As appeared in Fig.7, the locks can, separately, solidify the contributions of MUX-4 to MUX-7 or just those of MUX-6 to MUX-7 when the PP4 to PP7 or just the PP6 to PP7 are zeros to lessen the progress control dispersal. Such cases happen regularly in remote sight and sound information coding like surface coding, orthogonal recurrence division multiplexing, and channel outlines.

# 3.2. Applying the SPST to the Compression Tree

Fig. demonstrates the engineering chart for the proposed VMFU in which the SPST altered Booth encoder has been appeared in Fig. 10. The VMFU can be generally disintegrated into three areas, i.e., the Partial Product Generation, the Partial Product Reduction (PPR), and the Accumulation (ACC) segments. At the point when the operand other than the Booth encoded one has a little supreme esteem, there are chances to decrease the spurious power dispersed in the pressure tree in the PPR segment. As indicated by the examination of the expansion appeared in Figs. 3 and 9, we supplant a portion of the adders in the pressure tree of the VMFU, which include the PP0 to PP3, with the SPST-prepared adders. In addition, the viper in the ACC segment is likewise supplanted with the SPST-prepared snake. This snake is utilized to aggregate the increase brings about the MAC operation and register the interjection, SAD, expansion, and subtraction. These adders are set apart with diagonal lines as appeared in Fig. 11 with their bit widths of the MSP and LSP demonstrated, separately, in the numerator and the denominator of the nearing division esteems.

# 3.3. Freezing the Switching Activities of the Unused Circuits

The information streams of the VMFU are controlled by the appropriately organized multiplexers. By solidifying the unused circuits because of the choice of a specific sort of usefulness, inefficient exchanging power dissemination can be maintained a strategic distance from, as appeared in Fig.8. Furthermore, the circuits prompted by the SPST can be solidified to kill the SPST capacity of the VMFU. This choice might be valuable when the information don't have favourable highlights like the interactive media information on the grounds that the SPST may not contribute positive power sparing when both the info information are irregular.

Figure 8: Low power SPST equipped VMFU

### 4. Conclusion

Proposed a low-control system called SPST and investigates its applications in mixed media/DSP calculations, where the hypothetical examination and the acknowledgment issues of the SPST are completely talked about. The proposed SPST can clearly diminish the exchanging (or dynamic) control dissemination, which includes a critical part of the entire power dissipation in integrated circuits.

### **References**

- [1] A.P. Chandrakasan and R. W. Brodersen, "Minimizing power consumption in digital CMOS circuits," Proc. IEEE, vol. 83, Apr. 1995.

- [2] K. H. Chen, K. C. Chao, J. I. Guo, J. S. Wang, and Y. S. Chu, "Design exploration of a spurious power suppression technique (SPST) and its applications," in Proc. IEEE Asian Solid-State Circuits Conf., Hsinchu, Taiwan, Nov. 2005.

- [3] K. K. Parhi, "Approaches to low-power implementations of DSP systems," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 48, Oct. 2001.

- [4] K. H. Chen, K. C. Chao, J. I. Guo, J. S. Wang, and Y. S. Chu, "Design exploration of a spurious power suppression technique (SPST) and its applications," in Proc. IEEE Asian Solid-State Circuits Conf., Hsinchu, Taiwan, Nov. 2005.

E-mail address: drmsgaikwad@ gmail.com/barivishals@ gmail.com

<sup>\*</sup>Corresponding author.